|

|

RECHNERARCHITEKTUR WS 0203 - Vorlesung mit Übung

|

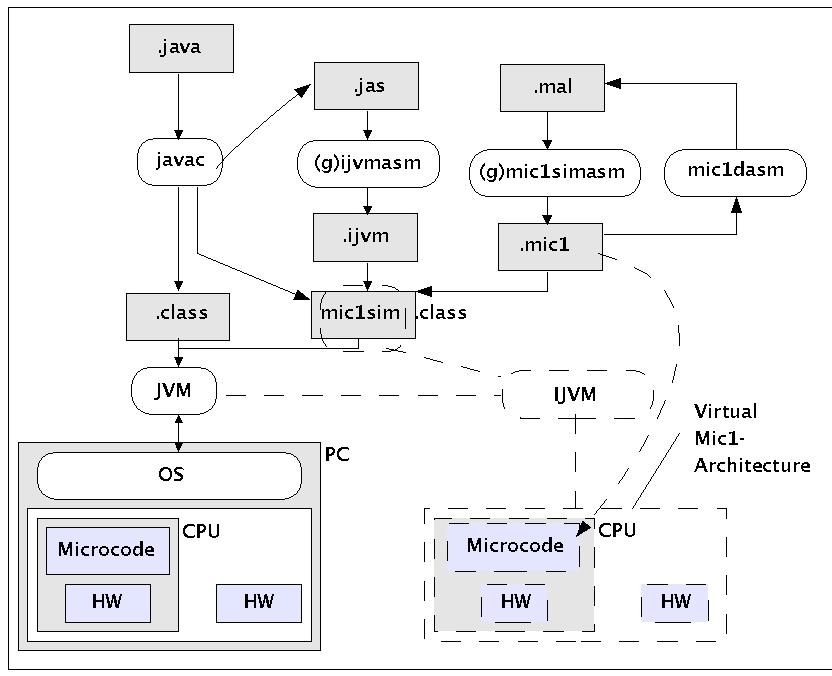

Benutzte Dateien

IJVM-Assembler

PC := Der Programmcounter zeigt auf den Methodenbereich, der als Bytebereich interpretiert wird; hier liegen die Programme. Jede Methode hat ihren Methodenbereich. die ersten 4 Bytes haben eine besondere Funktion: Bytes 1+2 = 16-Bit-Zahl, heben die Anzahl der Parameter für diese Methode an; Bytes 3+4 = 16-Bit-Zahl; die Grösse des lokalen Variablenrahmens ab LV.

LV := Lokaler Variablenrahmen; zeigt auf Wörter. Der lokale Variablenrahmen wird für jede Methode angelegt und enthält als erstes die Werte der übergebenen Parameter. Die Grösse des lokalen Variablenrahmens wird im Byte 3+4 des Methodenbereiches als 16-Bit-Zahl definiert.

SP := Stapelzeiger für Operandenstack; zeigt auf Wörter. SP zeigt immer auf den letzten Wert. Der Stapel beginnt unmittelbar nach dem lokalen Variablenrahmen.

Adressierung des Speichers als Bytes (4 GB) oder als 4-Byte-Wörter

CPP .= Zeiger auf Konstantenpool; zeigt auf Wörter; kann nicht geschrieben werden

PC := Der Programmcounter zeigt auf den Methodenbereich, der als Bytebereich interpretiert wird; hier liegen die Programme.

INVOKEVIRTUAl, IRETURN := Einrichten einer neuen Umgebung mit Möglichkeit der Rückkehr. Rückgabewert wird mitels Stack kommuniziert.

Das folgende Programm ist das aktuelle Mikroprogramm der simulierten IJVM-Mikroarchiektur, deassembliert aus der Binär-Datei, die der Simulator mic1sim liest, bevor er seine Simulation startet.

gerd@goedel:~/WEB-MATERIAL/fh/I-RA/MIC1SIM> java mic1dasm mic1ijvm.mic1 mic1dasm V0. 0 0x0: goto 0x2 0x1: PC=PC+1;goto 0x40 0x2: PC=PC+1;fetch;goto (MBR) 0x3: H=TOS;goto 0x4 0x4: TOS=MDR=H+MDR;wr;goto 0x2 0x5: H=TOS;goto 0x6 0x6: TOS=MDR=MDR-H;wr;goto 0x2 0x7: H=TOS;goto 0x8 0x8: TOS=MDR=H AND MDR;wr;goto 0x2 0x9: H=TOS;goto 0xA 0xa: TOS=MDR=H OR MDR;wr;goto 0x2 0xb: MDR=TOS;wr;goto 0x2 0xc: goto 0xD 0xd: TOS=MDR;goto 0x2 0xe: MAR=SP;goto 0xF 0xf: H=MDR;wr;goto 0x11 0x10: SP=MAR=SP+1;goto 0x16 0x11: MDR=TOS;goto 0x12 0x12: MAR=SP-1;wr;goto 0x14 0x13: PC=PC+1;fetch;goto 0x27 0x14: TOS=H;goto 0x2 0x15: H=LV;goto 0x18 0x16: PC=PC+1;fetch;goto 0x17 0x17: TOS=MDR=MBR;wr;goto 0x2 0x18: MAR=H+MBRU;rd;goto 0x19 0x19: SP=MAR=SP+1;goto 0x1A 0x1a: PC=PC+1;wr;fetch;goto 0x1B 0x1b: TOS=MDR;goto 0x2 0x1c: MAR=H+MBRU;goto 0x1D 0x1d: MDR=TOS;wr;goto 0x1E 0x1e: SP=MAR=SP-1;rd;goto 0x1F 0x1f: PC=PC+1;fetch;goto 0x20 0x20: TOS=MDR;goto 0x2 0x21: H=MBRU<<8;goto 0x22 0x22: H=H OR MBRU;goto 0x23 0x23: MAR=H+LV;rd;goto 0x19 0x24: H=MBRU<<8;goto 0x25 0x25: H=H OR MBRU;goto 0x26 0x26: MAR=H+LV;goto 0x1D 0x27: H=MBRU<<8;goto 0x28 0x28: H=H OR MBRU;goto 0x29 0x29: MAR=H+CPP;rd;goto 0x19 0x2a: MAR=H+MBRU;rd;goto 0x2B 0x2b: PC=PC+1;fetch;goto 0x2C 0x2c: H=MDR;goto 0x2D 0x2d: PC=PC+1;fetch;goto 0x2E 0x2e: MDR=H+MBR;wr;goto 0x2 0x2f: PC=PC+1;fetch;goto 0x30 0x30: H=MBR<<8;goto 0x31 0x31: H=H OR MBRU;goto 0x32 0x32: PC=H+OPC;fetch;goto 0x33 0x33: goto 0x2 0x34: OPC=TOS;goto 0x35 0x35: TOS=MDR;goto 0x37 0x36: H=LV;goto 0x1C 0x37: N=OPC;if (N) goto 0x101; else goto 0x1 0x38: OPC=TOS;goto 0x39 0x39: TOS=MDR;goto 0x3A 0x3a: Z=OPC;if (Z) goto 0x101; else goto 0x1 0x3b: SP=MAR=SP-1;goto 0x3C 0x3c: H=MDR;rd;goto 0x3D 0x3d: OPC=TOS;goto 0x3E 0x3e: TOS=MDR;goto 0x3F 0x3f: Z=OPC-H;if (Z) goto 0x101; else goto 0x1 0x40: PC=PC+1;fetch;goto 0x41 0x41: goto 0x2 0x42: H=MBRU<<8;goto 0x43 0x43: H=H OR MBRU;goto 0x44 0x44: MAR=H+CPP;rd;goto 0x45 0x45: OPC=PC+1;goto 0x46 0x46: PC=MDR;fetch;goto 0x47 0x47: PC=PC+1;fetch;goto 0x48 0x48: H=MBRU<<8;goto 0x49 0x49: H=H OR MBRU;goto 0x4A 0x4a: PC=PC+1;fetch;goto 0x4B 0x4b: TOS=SP-H;goto 0x4C 0x4c: TOS=MAR=TOS+1;goto 0x4D 0x4d: PC=PC+1;fetch;goto 0x4E 0x4e: H=MBRU<<8;goto 0x4F 0x4f: H=H OR MBRU;goto 0x50 0x50: MDR=H+SP+1;wr;goto 0x51 0x51: SP=MAR=MDR;goto 0x52 0x52: MDR=OPC;wr;goto 0x53 0x53: SP=MAR=SP+1;goto 0x54 0x54: MDR=LV;wr;goto 0x55 0x55: PC=PC+1;fetch;goto 0x56 0x56: LV=TOS;goto 0x2 0x57: SP=MAR=SP-1;rd;goto 0xC 0x58: goto 0x5A 0x59: SP=MAR=SP+1;goto 0xB 0x5a: LV=MAR=MDR;rd;goto 0x5B 0x5b: MAR=LV+1;goto 0x5C 0x5c: PC=MDR;rd;fetch;goto 0x5D 0x5d: MAR=SP;goto 0x5E 0x5e: LV=MDR;goto 0x61 0x5f: MAR=SP-1;rd;goto 0xE 0x60: SP=MAR=SP-1;rd;goto 0x3 0x61: MDR=TOS;wr;goto 0x2 0x62: OPC=H+OPC;goto 0x63 0x63: MAR=H+OPC;goto 0x65 0x64: SP=MAR=SP-1;rd;goto 0x5 0x65: H=OPC=1;goto 0x66 0x66: H=OPC=H+OPC;goto 0x67 0x67: H=OPC=H+OPC;goto 0x68 0x68: H=OPC=H+OPC;goto 0x69 0x69: H=OPC=H+OPC+1;goto 0x6A 0x6a: H=OPC=H+OPC;goto 0x6B 0x6b: MDR=H+OPC+1;wr;goto 0x6C 0x6c: H=OPC=1;goto 0x6D 0x6d: H=OPC=H+OPC;goto 0x6E 0x6e: H=OPC=H+OPC+1;goto 0x6F 0x6f: H=OPC=H+OPC;goto 0x70 0x70: H=OPC=H+OPC;goto 0x71 0x71: H=OPC=H+OPC+1;goto 0x72 0x72: MDR=H+OPC;wr;goto 0x73 0x73: goto 0x74 0x74: MDR=H+OPC;wr;goto 0x75 0x75: H=OPC=1;goto 0x76 0x76: H=OPC=H+OPC;goto 0x77 0x77: H=OPC=H+OPC;goto 0x78 0x78: H=OPC=H+OPC+1;goto 0x79 0x79: H=OPC=H+OPC+1;goto 0x7A 0x7a: H=OPC=H+OPC+1;goto 0x7B 0x7b: MDR=H+OPC+1;wr;goto 0x7C 0x7c: H=OPC=1;goto 0x7D 0x7d: H=OPC=H+OPC;goto 0x7F 0x7e: SP=MAR=SP-1;rd;goto 0x7 0x7f: H=OPC=H+OPC+1;goto 0x80 0x80: H=OPC=H+OPC;goto 0x81 0x81: H=OPC=H+OPC;goto 0x82 0x82: H=OPC=H+OPC+1;goto 0x83 0x83: MDR=H+OPC;wr;goto 0x85 0x84: H=LV;goto 0x2A 0x85: goto 0xFF 0x86: OPC=H+OPC;goto 0x87 0x87: MAR=H+OPC;goto 0x88 0x88: MDR=TOS;wr;goto 0x89 0x89: goto 0x8A 0x8a: SP=MAR=SP-1;rd;goto 0x8B 0x8b: goto 0x8C 0x8c: TOS=MDR;goto 0x2 0x8d: OPC=H+OPC;goto 0x8E 0x8e: MAR=H+OPC;rd;goto 0x8F 0x8f: SP=MAR=SP+1;goto 0x90 0x90: TOS=MDR;wr;goto 0x2 0x91: goto 0xFE ... 0x98: goto 0xFE 0x99: SP=MAR=SP-1;rd;goto 0x38 0x9a: goto 0xFE 0x9b: SP=MAR=SP-1;rd;goto 0x34 0x9c: goto 0xFE ... 0x9e: goto 0xFE 0x9f: SP=MAR=SP-1;rd;goto 0x3B 0xa0: goto 0xFE ... 0xa6: goto 0xFE 0xa7: OPC=PC-1;goto 0x2F 0xa8: goto 0xFE ... 0xab: goto 0xFE 0xac: SP=MAR=LV;rd;goto 0x58 0xad: goto 0xFE ... 0xaf: goto 0xFE 0xb0: SP=MAR=SP-1;rd;goto 0x9 0xb1: goto 0xFE ... 0xb5: goto 0xFE 0xb6: PC=PC+1;fetch;goto 0x42 0xb7: goto 0xFE ... 0xc4: PC=PC+1;fetch;goto (MBR OR 0x100) 0xc5: goto 0xFE ... 0xfc: H=OPC=-1;goto 0x8D 0xfd: H=OPC=-1;goto 0x86 0xfe: H=OPC=-1;goto 0x62 0xff: goto 0xFF 0x100: goto 0xFE 0x101: OPC=PC-1;fetch;goto 0x2F 0x102: goto 0xFE ... 0x114: goto 0xFE 0x115: PC=PC+1;fetch;goto 0x21 0x116: goto 0xFE ... 0x135: goto 0xFE 0x136: PC=PC+1;fetch;goto 0x24 0x137: goto 0xFE ... 0x1ff: goto 0xFE

Das vorausgehende deassemblierte Programm wird im Folgenden nochmals ausführlicher dargestellt und kommentiert. Die Zuordnung zwischen den Befehlen der IJVM-Assemblersprache und dem Mikrocode der simulierten IJVM-Mikroarchitektur wird eutlicher:

// note that this is nearly identical to the example

// given in Tanenbaum. Note:

//

// 1) SlashSlash-style ("//") comment characters have been added.

//

// 2) "nop" has been added as a pseudo-instruction to indicate that

// nothing should be done except goto the next instruction. It

// is a do-nothing sub-instruction that allows us to have MAL

// statements without a label.

//

// 3) instructions are "anchored" to locations in the control

// store as defined below with the ".label" pseudo-instruction

//

// 4) a default instruction may be specified using the ".default"

// pseudo-instruction. This instruction is placed in all

// unused locations of the control store by the mic1 MAL assembler.

//

// labeled statements are "anchored" at the specified control store address

.label nop1 0x00

.label bipush1 0x10

.label ldc_w1 0x13

.label iload1 0x15

.label wide_iload1 0x115

.label istore1 0x36

.label wide_istore1 0x136

.label pop1 0x57

.label dup1 0x59

.label swap1 0x5F

.label iadd1 0x60

.label isub1 0x64

.label iand1 0x7E

.label iinc1 0x84

.label ifeq1 0x99

.label iflt1 0x9B

.label if_icmpeq1 0x9F

.label goto1 0xA7

.label ireturn1 0xAC

.label ior1 0xB0

.label invokevirtual1 0xB6

.label wide1 0xC4

.label halt1 0xFF

.label err1 0xFE

.label out1 0xFD

.label in1 0xFC

// default instruction to place in any unused addresses of the control store

.default goto err1

Main1 PC = PC + 1; fetch; goto (MBR) // MBR holds opcode; get next byte; dispatch

nop1 goto Main1 // Do nothing

iadd1 MAR = SP = SP - 1; rd // Read in next-to-top word on stack

iadd2 H = TOS // H = top of stack

iadd3 MDR = TOS = MDR + H; wr; goto Main1 // Add top two words; write to top of stack

isub1 MAR = SP = SP - 1; rd // Read in next-to-top word on stack

isub2 H = TOS // H = top of stack

isub3 MDR = TOS = MDR - H; wr; goto Main1 // Do subtraction; write to top of stack

iand1 MAR = SP = SP - 1; rd // Read in next-to-top word on stack

iand2 H = TOS // H = top of stack

iand3 MDR = TOS = MDR AND H; wr; goto Main1 // Do AND; write to new top of stack

ior1 MAR = SP = SP - 1; rd // Read in next-to-top word on stack

ior2 H = TOS // H = top of stack

ior3 MDR = TOS = MDR OR H; wr; goto Main1 // Do OR; write to new top of stack

dup1 MAR = SP = SP + 1 // Increment SP and copy to MAR

dup2 MDR = TOS; wr; goto Main1 // Write new stack word

pop1 MAR = SP = SP - 1; rd // Read in next-to-top word on stack

pop2 // Wait for new TOS to be read from memory

pop3 TOS = MDR; goto Main1 // Copy new word to TOS

swap1 MAR = SP - 1; rd // Set MAR to SP - 1; read 2nd word from stack

swap2 MAR = SP // Set MAR to top word

swap3 H = MDR; wr // Save TOS in H; write 2nd word to top of stack

swap4 MDR = TOS // Copy old TOS to MDR

swap5 MAR = SP - 1; wr // Set MAR to SP - 1; write as 2nd word on stack

swap6 TOS = H; goto Main1 // Update TOS

bipush1 SP = MAR = SP + 1 // MBR = the byte to push onto stack

bipush2 PC = PC + 1; fetch // Increment PC, fetch next opcode

bipush3 MDR = TOS = MBR; wr; goto Main1 // Sign-extend constant and push on stack

iload1 H = LV // MBR contains index; copy LV to H

iload2 MAR = MBRU + H; rd // MAR = address of local variable to push

iload3 MAR = SP = SP + 1 // SP points to new top of stack; prepare write

iload4 PC = PC + 1; fetch; wr // Inc PC; get next opcode; write top of stack

iload5 TOS = MDR; goto Main1 // Update TOS

istore1 H = LV // MBR contains index; Copy LV to H

istore2 MAR = MBRU + H // MAR = address of local variable to store into

istore3 MDR = TOS; wr // Copy TOS to MDR; write word

istore4 SP = MAR = SP - 1; rd // Read in next-to-top word on stack

istore5 PC = PC + 1; fetch // Increment PC; fetch next opcode

istore6 TOS = MDR; goto Main1 // Update TOS

wide1 PC = PC + 1; fetch; goto (MBR OR 0x100) // Multiway branch with high bit set

wide_iload1 PC = PC + 1; fetch // MBR contains 1st index byte; fetch 2nd

wide_iload2 H = MBRU << 8 // H = 1st index byte shifted left 8 bits

wide_iload3 H = MBRU OR H // H = 16-bit index of local variable

wide_iload4 MAR = LV + H; rd; goto iload3 // MAR = address of local variable to push

wide_istore1 PC = PC + 1; fetch // MBR contains 1st index byte; fetch 2nd

wide_istore2 H = MBRU << 8 // H = 1st index byte shifted left 8 bits

wide_istore3 H = MBRU OR H // H = 16-bit index of local variable

wide_istore4 MAR = LV + H; goto istore3 // MAR = address of local variable to store into

ldc_w1 PC = PC + 1; fetch // MBR contains 1st index byte; fetch 2nd

ldc_w2 H = MBRU << 8 // H = 1st index byte << 8

ldc_w3 H = MBRU OR H // H = 16-bit index into constant pool

ldc_w4 MAR = H + CPP; rd; goto iload3 // MAR = address of constant in pool

iinc1 H = LV // MBR contains index; Copy LV to H

iinc2 MAR = MBRU + H; rd // Copy LV + index to MAR; Read variable

iinc3 PC = PC + 1; fetch // Fetch constant

iinc4 H = MDR // Copy variable to H

iinc5 PC = PC + 1; fetch // Fetch next opcode

iinc6 MDR = MBR + H; wr; goto Main1 // Put sum in MDR; update variable

goto1 OPC = PC - 1 // Save address of opcode.

goto2 PC = PC + 1; fetch // MBR = 1st byte of offset; fetch 2nd byte

goto3 H = MBR << 8 // Shift and save signed first byte in H

goto4 H = MBRU OR H // H = 16-bit branch offset

goto5 PC = OPC + H; fetch // Add offset to OPC

goto6 goto Main1 // Wait for fetch of next opcode

iflt1 MAR = SP = SP - 1; rd // Read in next-to-top word on stack

iflt2 OPC = TOS // Save TOS in OPC temporarily

iflt3 TOS = MDR // Put new top of stack in TOS

iflt4 N = OPC; if (N) goto T; else goto F // Branch on N bit

ifeq1 MAR = SP = SP - 1; rd // Read in next-to-top word of stack

ifeq2 OPC = TOS // Save TOS in OPC temporarily

ifeq3 TOS = MDR // Put new top of stack in TOS

ifeq4 Z = OPC; if (Z) goto T; else goto F // Branch on Z bit

if_icmpeq1 MAR = SP = SP - 1; rd // Read in next-to-top word of stack

if_icmpeq2 MAR = SP = SP - 1 // Set MAR to read in new top-of-stack

if_icmpeq3 H = MDR; rd // Copy second stack word to H

if_icmpeq4 OPC = TOS // Save TOS in OPC temporarily

if_icmpeq5 TOS = MDR // Put new top of stack in TOS

if_icmpeq6 Z = OPC - H; if (Z) goto T; else goto F // If top 2 words are equal, goto T, else goto F

T OPC = PC - 1; fetch; goto goto2 // Same as goto1; needed for target address

F PC = PC + 1 // Skip first offset byte

F2 PC = PC + 1; fetch // PC now points to next opcode

F3 goto Main1 // Wait for fetch of opcode

invokevirtual1 PC = PC + 1; fetch // MBR = index byte 1; inc. PC, get 2nd byte

invokevirtual2 H = MBRU << 8 // Shift and save first byte in H

invokevirtual3 H = MBRU OR H // H = offset of method pointer from CPP

invokevirtual4 MAR = CPP + H; rd // Get pointer to method from CPP area

invokevirtual5 OPC = PC + 1 // Save Return PC in OPC temporarily

invokevirtual6 PC = MDR; fetch // PC points to new method; get param count

invokevirtual7 PC = PC + 1; fetch // Fetch 2nd byte of parameter count

invokevirtual8 H = MBRU << 8 // Shift and save first byte in H

invokevirtual9 H = MBRU OR H // H = number of parameters

invokevirtual10 PC = PC + 1; fetch // Fetch first byte of # locals

invokevirtual11 TOS = SP - H // TOS = address of OBJREF - 1

invokevirtual12 TOS = MAR = TOS + 1 // TOS = address of OBJREF (new LV)

invokevirtual13 PC = PC + 1; fetch // Fetch second byte of # locals

invokevirtual14 H = MBRU << 8 // Shift and save first byte in H

invokevirtual15 H = MBRU OR H // H = # locals

invokevirtual16 MDR = SP + H + 1; wr // Overwrite OBJREF with link pointer

invokevirtual17 MAR = SP = MDR; // Set SP, MAR to location to hold old PC

invokevirtual18 MDR = OPC; wr // Save old PC above the local variables

invokevirtual19 MAR = SP = SP + 1 // SP points to location to hold old LV

invokevirtual20 MDR = LV; wr // Save old LV above saved PC

invokevirtual21 PC = PC + 1; fetch // Fetch first opcode of new method.

invokevirtual22 LV = TOS; goto Main1 // Set LV to point to LV Frame

ireturn1 MAR = SP = LV; rd // Reset SP, MAR to get link pointer

ireturn2 // Wait for read

ireturn3 LV = MAR = MDR; rd // Set LV to link ptr; get old PC

ireturn4 MAR = LV + 1 // Set MAR to read old LV

ireturn5 PC = MDR; rd; fetch // Restore PC; fetch next opcode

ireturn6 MAR = SP // Set MAR to write TOS

ireturn7 LV = MDR // Restore LV

ireturn8 MDR = TOS; wr; goto Main1 // Save return value on original top of stack

halt1 goto halt1

err1 OPC=H=-1

OPC=H+OPC

MAR=H+OPC // compute IO address

OPC=H=1 // 1

OPC=H=H+OPC // 10

OPC=H=H+OPC // 100

OPC=H=H+OPC // 1000

OPC=H=H+OPC+1 // 10001

OPC=H=H+OPC // 100010

MDR=H+OPC+1;wr // 1000101 'E'

OPC=H=1 // 1

OPC=H=H+OPC // 10

OPC=H=H+OPC+1 // 101

OPC=H=H+OPC // 1010

OPC=H=H+OPC // 10100

OPC=H=H+OPC+1 // 101001

MDR=H+OPC;wr // 1010010 'R'

nop

MDR=H+OPC;wr // 1010010 'R'

OPC=H=1 // 1

OPC=H=H+OPC // 10

OPC=H=H+OPC // 100

OPC=H=H+OPC+1 // 1001

OPC=H=H+OPC+1 // 10011

OPC=H=H+OPC+1 // 100111

MDR=H+OPC+1;wr // 1001111 'O'

OPC=H=1 // 1

OPC=H=H+OPC // 10

OPC=H=H+OPC+1 // 101

OPC=H=H+OPC // 1010

OPC=H=H+OPC // 10100

OPC=H=H+OPC+1 // 101001

MDR=H+OPC;wr // 1010010 'R'

goto halt1

out1 OPC=H=-1

OPC=H+OPC

MAR=H+OPC // compute OUT address

MDR=TOS; wr // write to output

nop

MAR=SP=SP-1; rd // decrement stack pointer

nop

TOS=MDR; goto Main1

in1 OPC=H=-1

OPC=H+OPC

MAR=H+OPC;rd // compute IN address ; read from input

MAR=SP=SP+1 // increment SP; wait for read

TOS=MDR;wr ; goto Main1 // Write

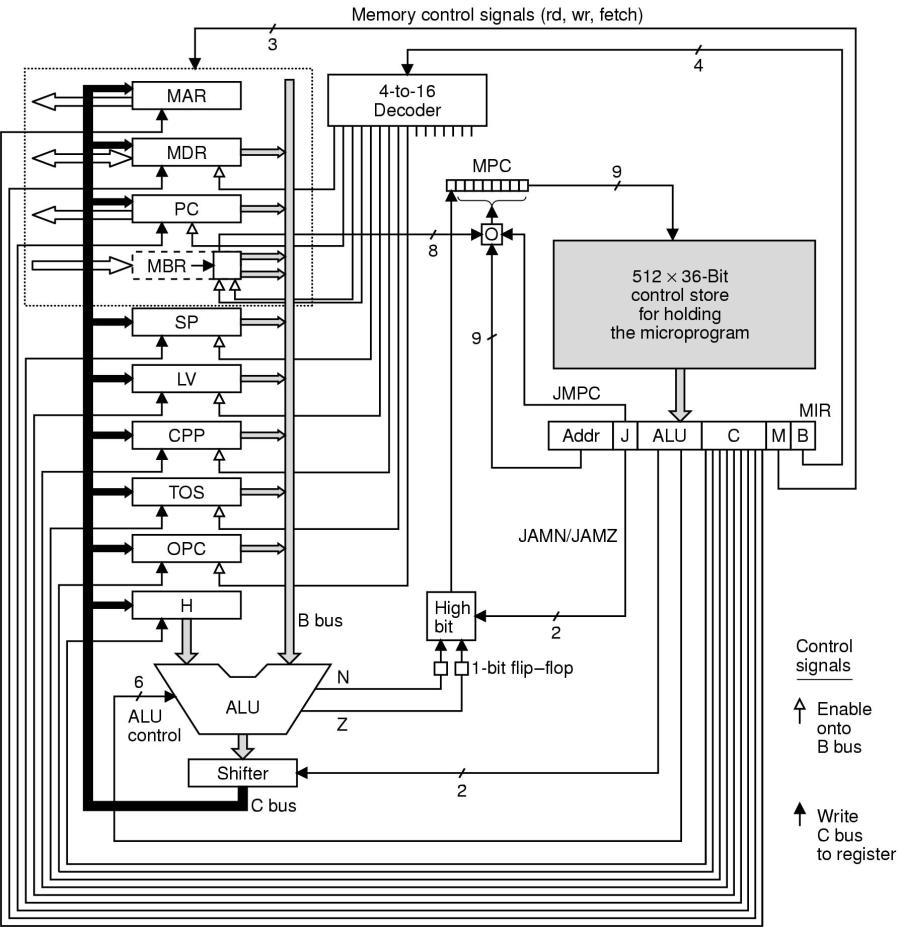

Microarchitecture

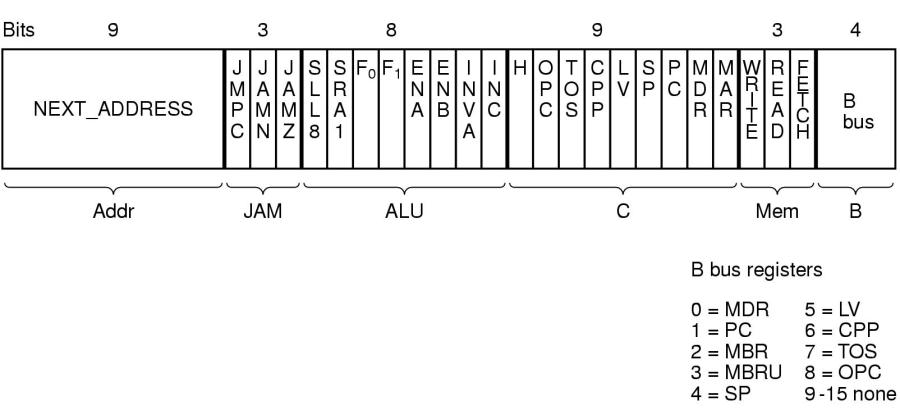

Format of one Command of the Micro Code

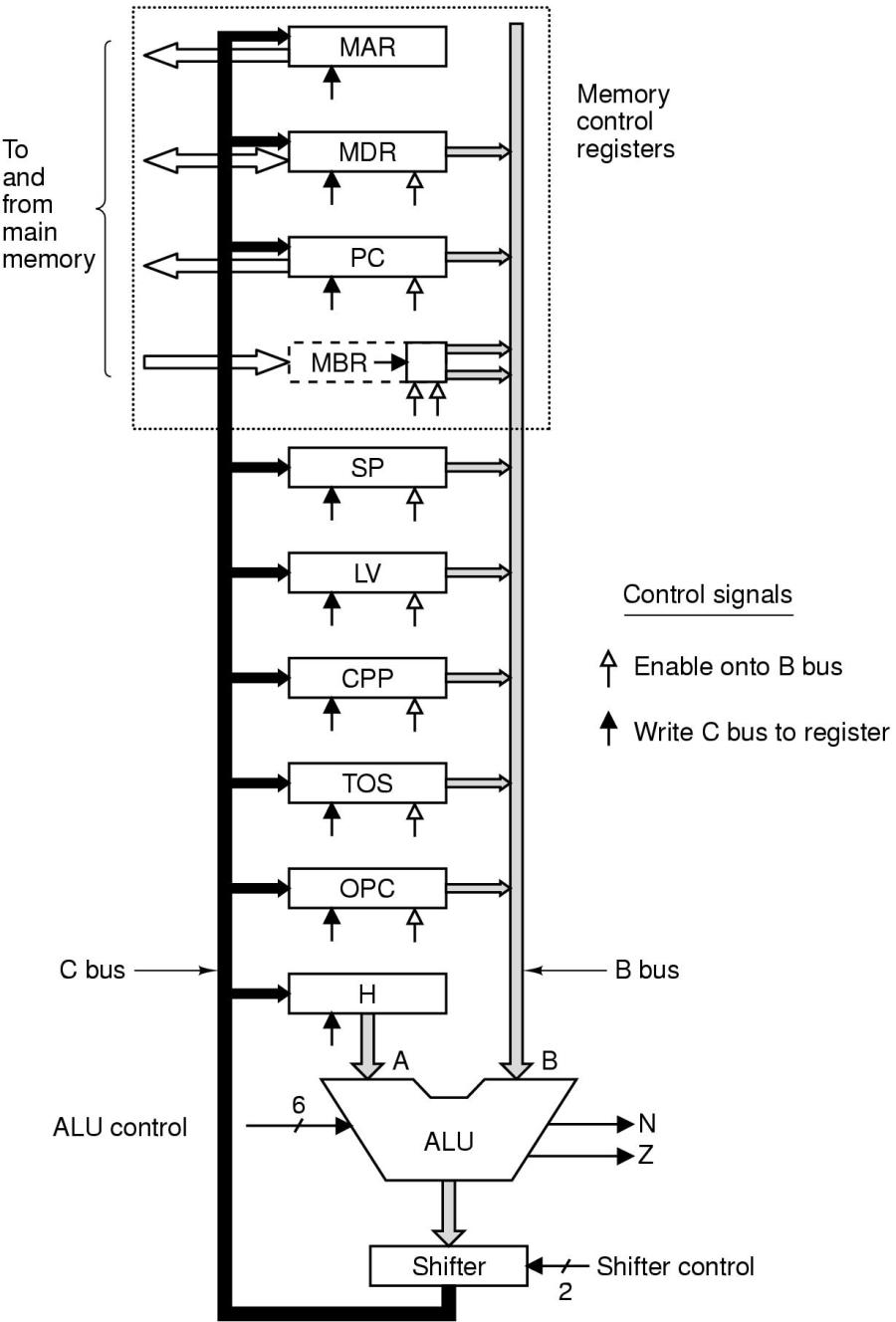

Register, ALU und Datenpfade

Buszyklen zur Teuerung der Operationen

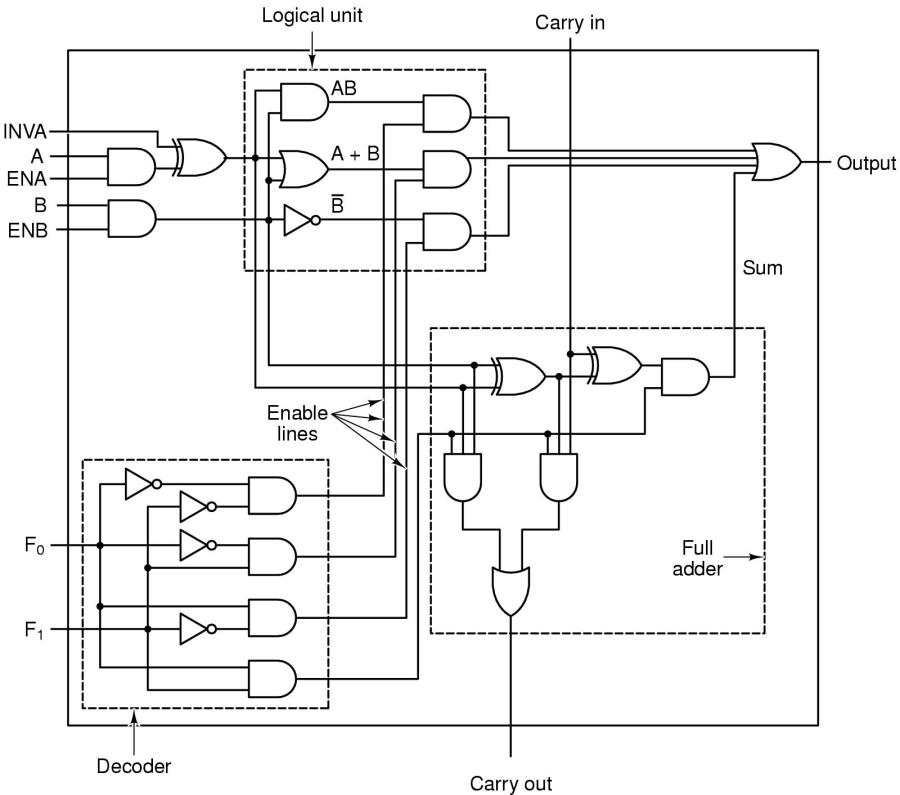

1-Bit-ALU (x Anzahl Bits)

SOURCE = Quellen für die ALU am B-Bus = {MAR, MDR, PC, MBR, MBRU, SP, LV, CPP, TOS, OPC} (MBRU := unsigned MBR). Zusätzlich kann die ALU natürlich H direkt lesen.

DEST = Mögliche Ziele für die ALU-Ausgabe am C-Bus = {MAR, MDR, PC, SP, LV, CPP, TOS, OPC, H }

Zusätzliche Qualifikationen: rd := read, wr := write von Wörtern, fetch := Holen eines Bytes. Dabei ist zu beachten, dass das Lesen/ SChreiben von Wörtern sowie das Holen eines Bytes parallel ablaufen können!

Die Ausgaben der ALU können vor Erreichung des Zieles (DEST) auch noch geshiftet werden ('<<8').

Z und N sind zwei imaginäre Register:

Z = TOS; if (Z) goto L1; else goto L2

goto (MBR OR Wert)

|

ALLE ZULÄSSIGEN OPERATIONEN |

|

DEST = H |

|

DEST = SOURCE |

|

DEST = ¬(SOURCE) |

|

DEST = H + SOURCE |

|

DEST = H + SOURCE + 1 |

|

DEST = H + 1 |

|

DEST = SOURCE + 1 |

|

DEST = SOURCE - H |

|

DEST = SOURCE - 1 |

|

DEST = -H |

|

DEST = H AND SOURCE |

|

DEST = H OR SOURCE |

|

DEST = 0 |

|

DEST = 1 |

|

DEST = -1 |

Was sind die Quellen für die ALU am B-Bus? (SOURCE)

Was sind die Ziele der ALU am C-Bus? (DESTINATION)

Welche Operationen kann die ALU mit den empfangenen Daten ausführen?

Welche Signale kann die ALU erzeugen?

Auf welche Weise kann das Ergebnis der ALU nochmals beeinflusst werden?

Wie können die Ergebnisse der ALU die Adressierung des nächsten Mikrocode-Befehles beeinflussen?

Welche Komponenten bestimmen die Adresse des nächsten Mikrocode-Befehles im MPC?

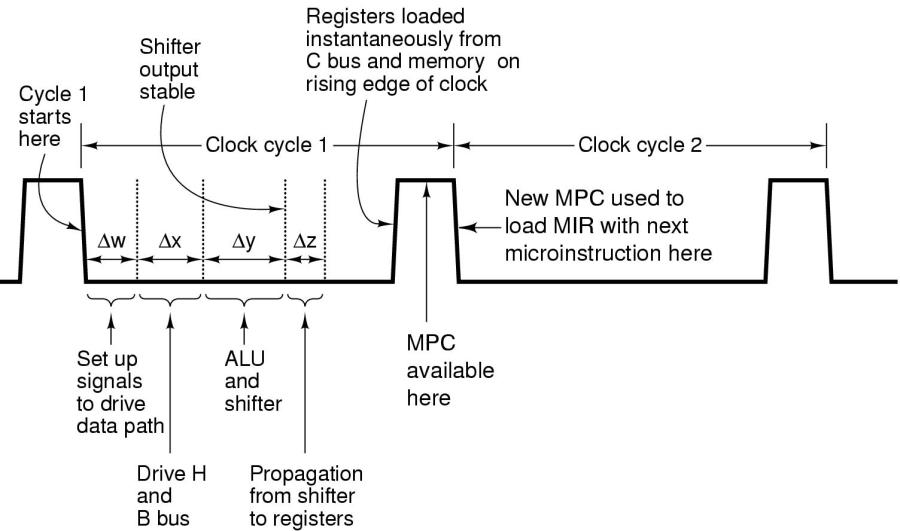

Was ist ein Mikro-Zyklus?

Was passiert mit den Signalen, die von einem Mikrobefehl gesetzt werden, innerhalb eines Mikro-Zyklus?

Wie greift die Hardware auf den Speicher zu?

Was ist der Unterschied zwischen Wortadressierung und Byteaddressierung? Welche Register sind bei der Wortadressierung beteiligt und welche bei der Byteadressierung?

Welche Funktion haben die Register CPP, LV, SP und PC?

Welche Funktion haben die Register MBR und MPC

Welche Funktion hat das Register H?

Welche Funktion haben die Register MAR und MDR?

Was muss passieren, damit ein IJVM-Assemblerbefehl im RAM, der in Byteformat vorliegt, über das MPC-Register einen bestimmten Mikrobefehl aktiviert?

Nehmen Sie sich die Mikroassemblerbefehle vor und versuchen sie zu verstehen, welche Vorgänge diesen im Bereich der Hardware-Architektur entsprechen.