|

|

RECHNERARCHITEKTUR WS 0203 - Vorlesung mit Übung

|

In der Vorlesung wurden die Überlegungen zu möglichen Optimierungsmassnahmen durch Vorstellen der Befehlsdekodierung und der Einführung zusätzlicher Cache-Speicher abgeschlossen. Es folgte dann ein erster Ausblick auf eine konkrete CPU, nämlich auf den Pentium-II Chip von Intel.

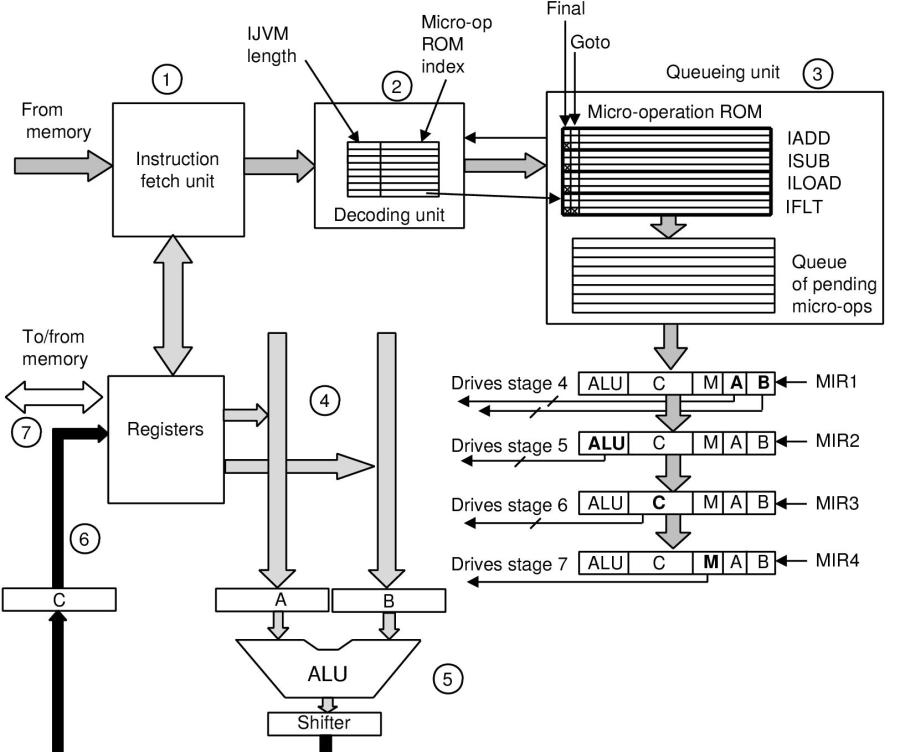

Simulator mic4 mit 7-stufiger Pipeline

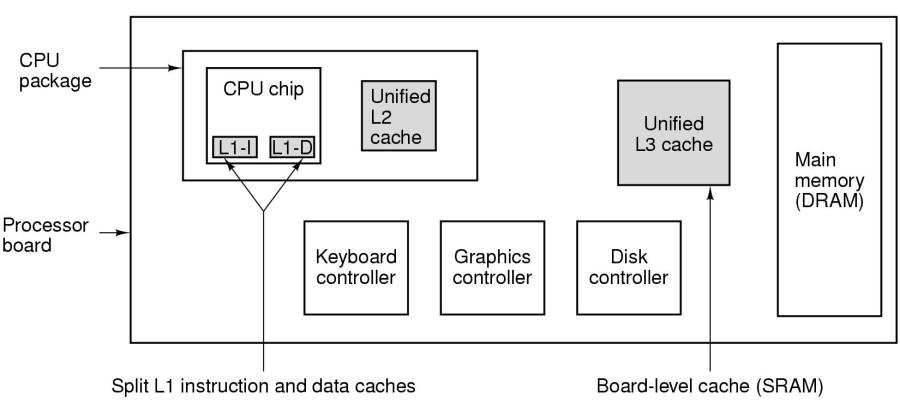

Mehr als ein Cache: Level 1 -3

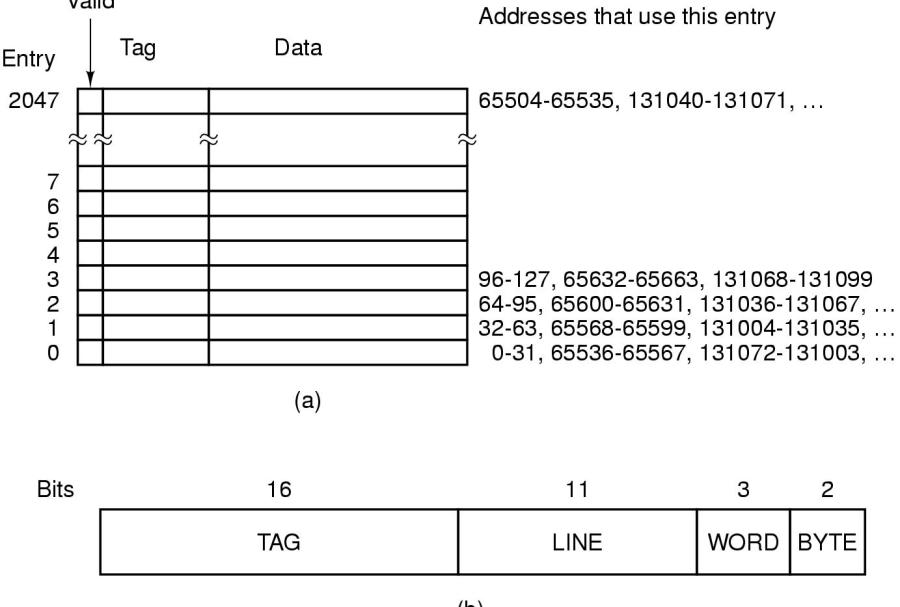

Direkt abgebildeter Cache

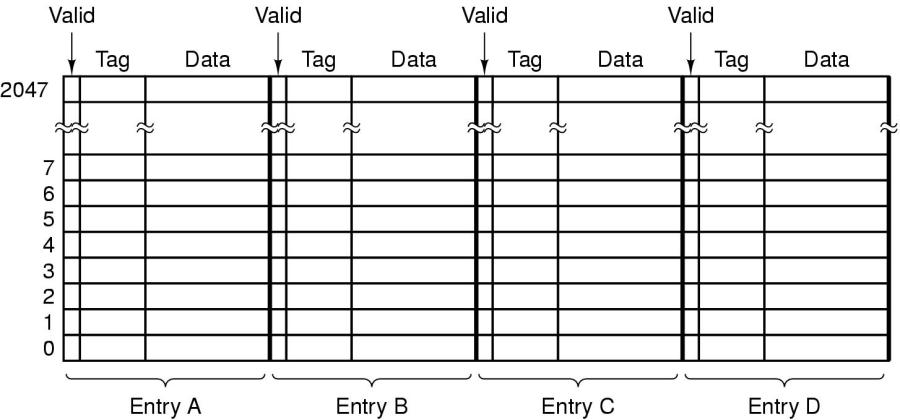

Teilassoziativer 4-Wege-Cache

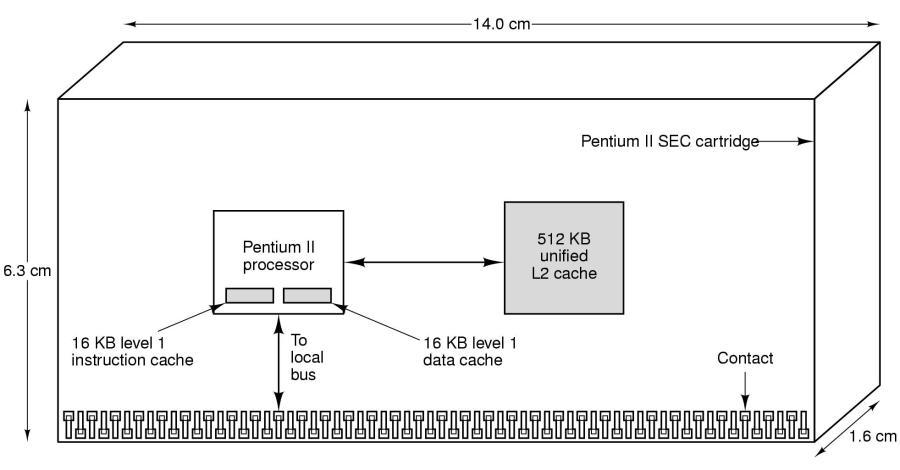

SEC des Pentium II

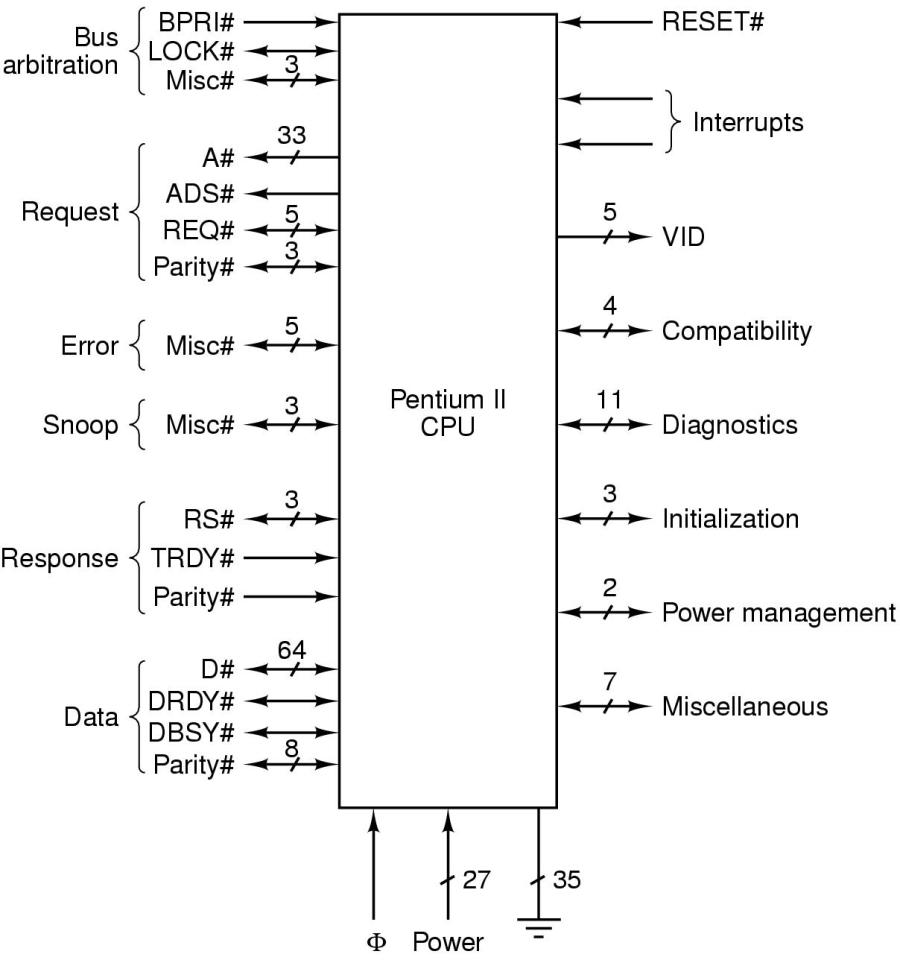

Pinbelegung des Pentium II

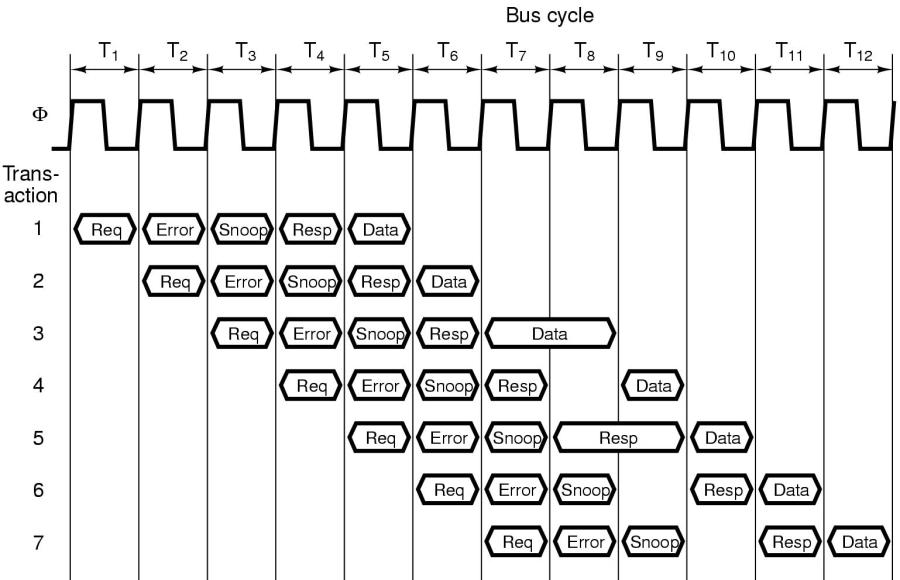

Pentium II Pipelining

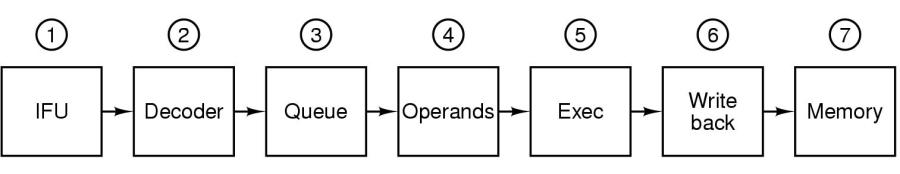

mic4: 7-stufige Pipeline

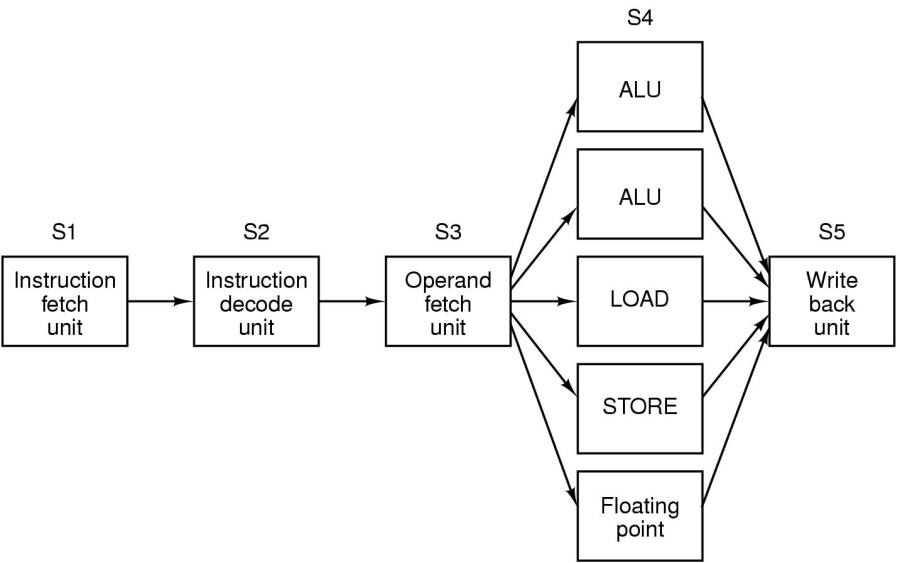

Superskalare Pipeline

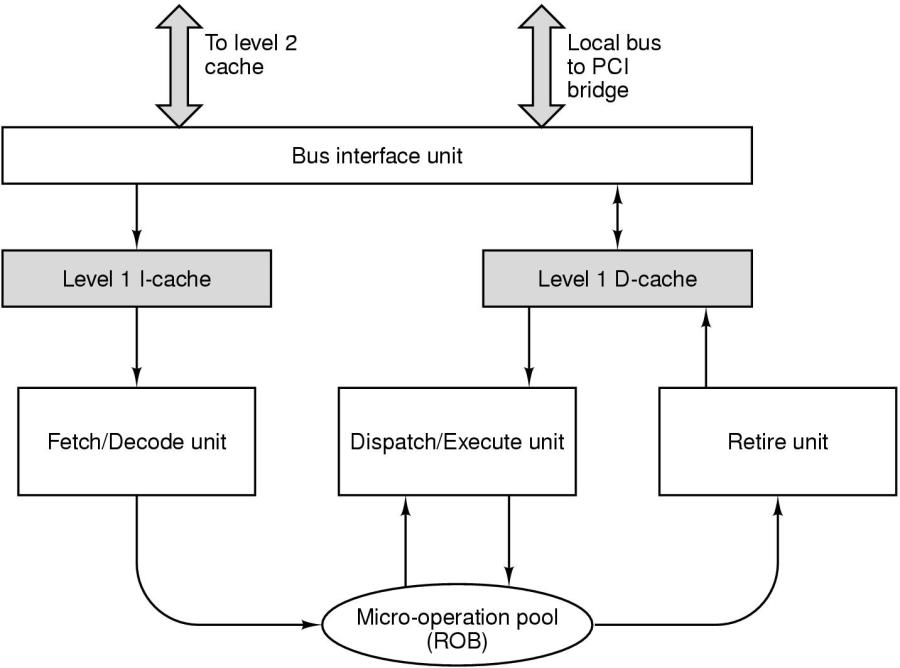

Pentium II Überblick

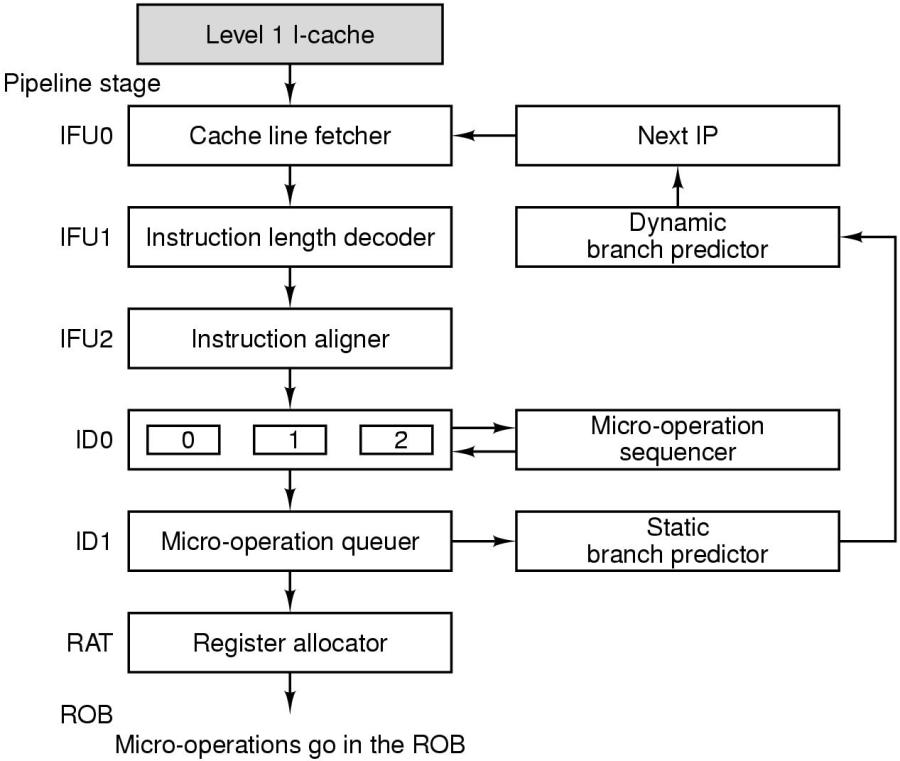

Pentium II IFU und DECODE

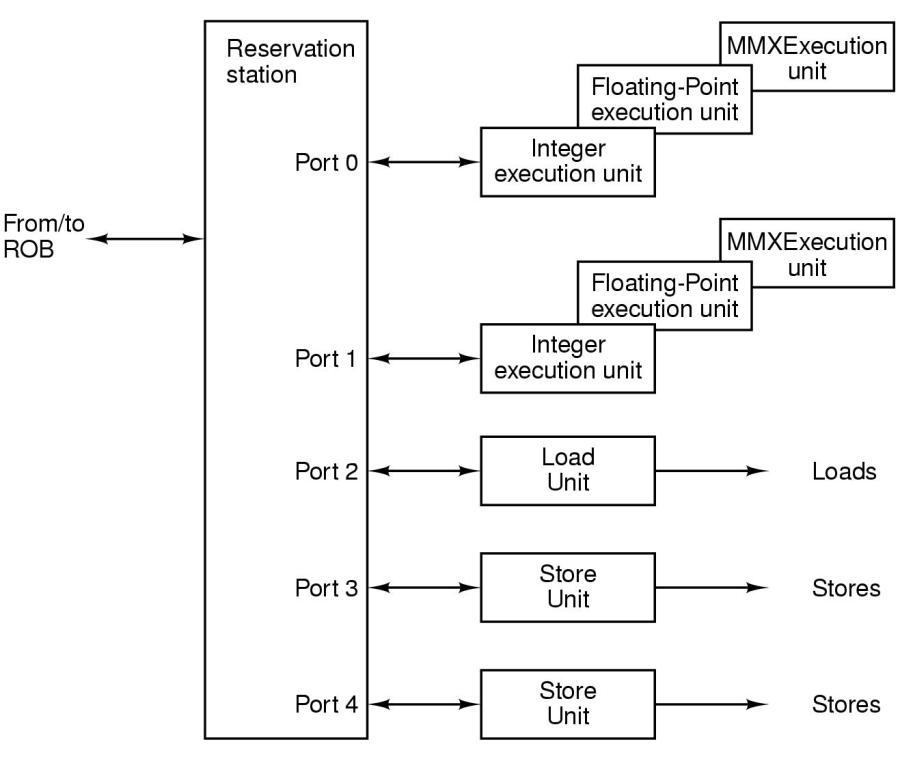

Pentium II DISPATCH/EXECUTE

In den Übungen