|

|

RECHNERARCHITEKTUR WS 04 |

Bis zu diesem Zeitpunkt wurde aufgezeigt, wie der Weg vom Grundlagenstreit in der Mathematik über das logische Konzept des Automaten zur technischen Realisierung von Automatenzuständen geführt hat. Es wurde kurz die Struktur von technischen Signalen erläutert, soweit dies für die Ebene der Schaltlogik und der darauf aufbauenden logischen Funktionen von Bedeutung ist. Die Grundbegriffe boolscher Funktionen wurden erläutert und wie man mit diesem Ausdrucksmittel die Struktur von logischen Schaltungen beschreiben und deren Verhalten ansatzweise berechnen kann.

Das nächste Ziel in der Darstellung besteht darin, ein Verständnis von Aufbau und von der Funktionsweise von Mikroprozessoren zu bekommen. Als Vorbereitung dazu sollen heute einige grundsätzliche Schaltungstypen vorgestellt werden: Adressierung, Addition und Speicherung.

Die verwendeten Schaltbilder sind bis auf die letzten Diagramme zum Thema D-Flipflop alle dem Buch von [TANENBAUM 2001] entnommen, der diese Schaltbilder freundlicherweise zur Verfügung stellt.

Ausgangslage der nachfolgenden Überlegung ist die Situation, dass ein Mikroprozessor aus verschiedenen Modulen bestehen wird, zwischen denen Daten hin- und hergeschoben werden müssen. Zu diesem Zweck müssen die einzelnen Module eindeutig selektiert werden können. Im folgenden werden drei einfache Beispiele gezeigt, wie eine solche Selektion realisiert werden kann.

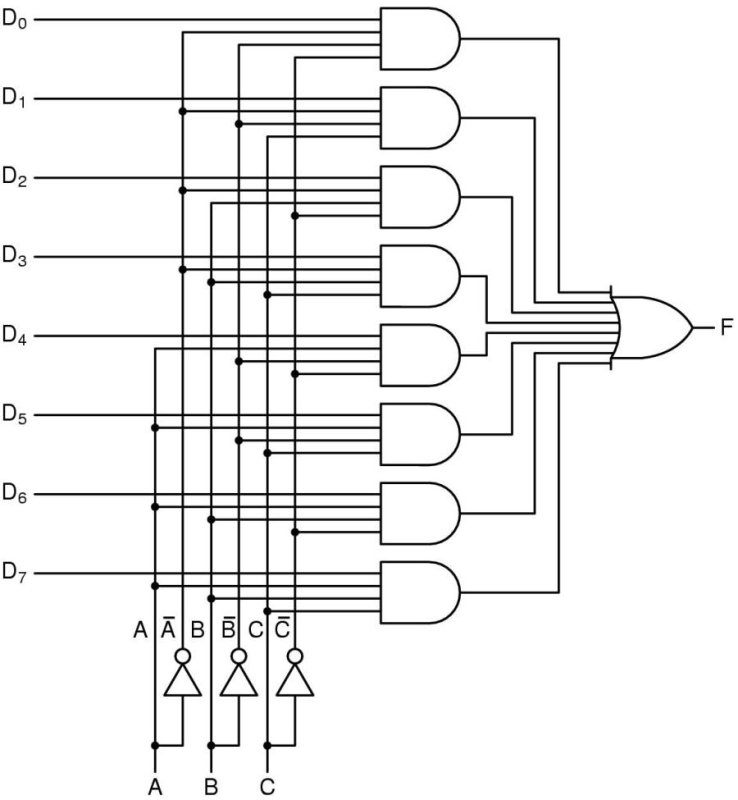

In der Multiplexer-Schaltung gibt es 8 Datenleitungen, von denen zu einem bestimmten Zeitpunkt genau eine auf den Ausgang F geschaltet werden soll. Als Hilfsmittel für die Auswahl stehen 3 Adressleitungen A,B und C zur Verfügung, die jeweils auch negiert (invertiert) werden. Am Beispiel der Datenleitung D0 kann man das Prinzip der Schaltung erkennen. Die Datenleitung D0 wird auf ein UND-Gatter ('AND') geführt, in dem noch drei weitere Leitungen enden, nämlich ~A, ~B und ~C. Dies bedeutet, die Signale von D0 können nur dann nach F weitergeleitet werden, wenn ~A, ~B und ~C jeweils den Wert 'H' bzw. '1' besitzen.

Multiplexer

2f-Multiplexer

2f-Multiplexer

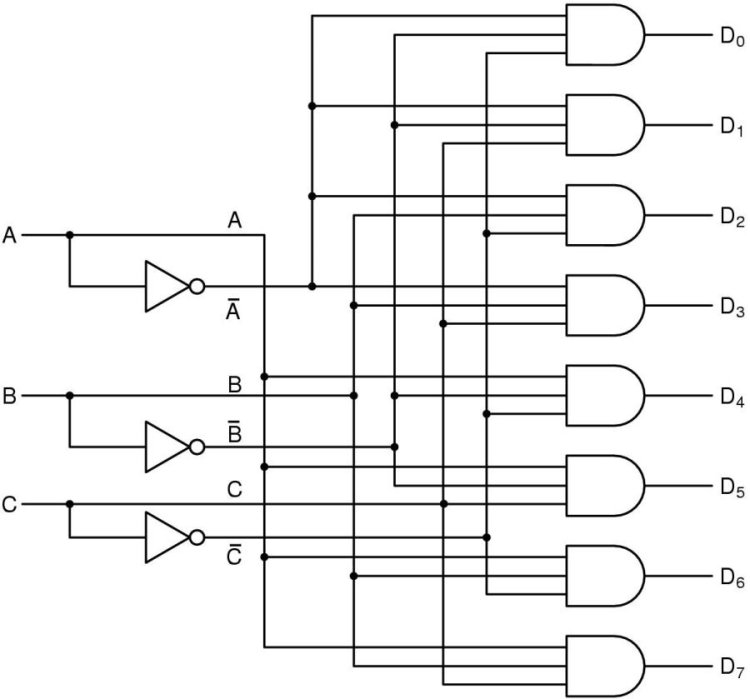

Eine andere Methode, zu selektieren, besteht in einem n-zu-m-Kodierer, hier am Beispiel eines 3-zu-8 Kodierers. Ausgehend von drei Eingangssignalen A,B und C zusammen mit deren Invertierungen wird eine von 8 Datenleitungen selektiert. Die Schaltlogik für die Auswahl einer bestimmten Datenleitung ist die gleiche wie im Beispiel mit dem Multiplexer, ausser, dass hier neben den Auswahlleitungen A,B und C keine weiteren Leitungen mehr benutzt werden.

3-zu-8 Dekodierer

2-zu-4 Dekodierer

2-zu-4 Dekodierer

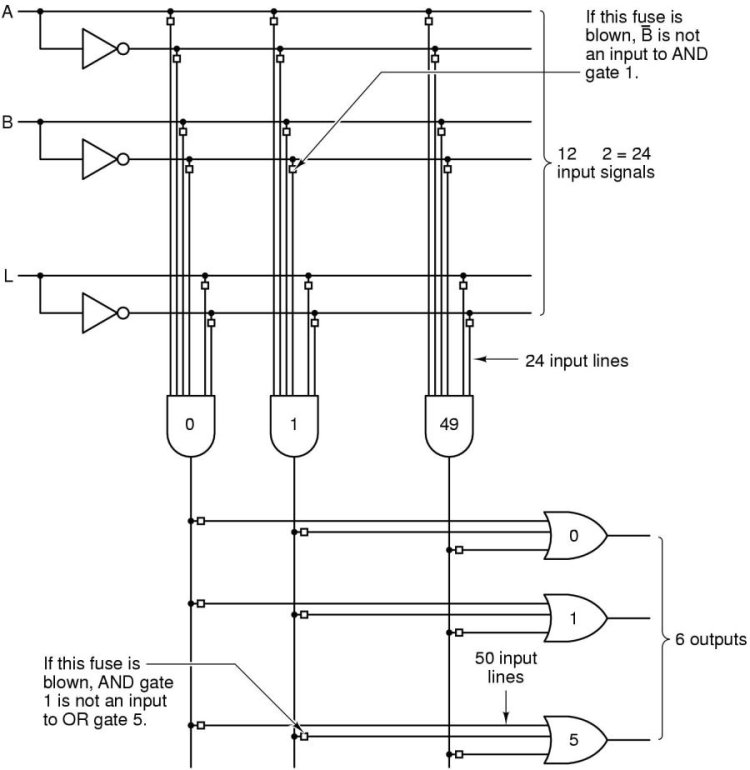

Wie schon diese einfachen Beispiele zeigen, kann der Aufwand an Gattern recht schnell sehr gross werden. Solche Schaltungen zu realisieren kostet dann vor allem viel Platz. Für Anwender bietet die Industrie heute für diese Zwecke eine Vielzahl von sogenannten Programmierbaren Logikbausteinen ('PLD := Programmable Logic Devices') an. Unter dem Obergebgriff der PLDs gibt es mittlerweile einige Unterbegriffe, wie z.B. den der Programmierbaren Logik Arrays ('PLA := Programmable Logic Arrays') (Für eine kleine Liste aktueller Begriffe im Umfeld von PLDs siehe [NÜHRMANN 1998:3735f]). Die Anzahl der auf diese Weise verfügbaren Gatter kann bis zu mehreren 1.000 umfassen. Die nachfolgende einfache Schaltung mit 60 Gattern verdeutlicht das Prinzip.

Diese Schaltung besitzt 12 Eingänge A, B, ..., L mit jeweils Invertierung, also 24 Eingangssignalen. Weiterhin werden 50 UND-Gatter angeboten; jedes dieser UND-Gatter ist mit allen 24 Eingangssignalen verbunden. Da in jeder dieser 24 Verbindungsleitungen eine Sicherung eingebaut ist kann der Anwender (mit der entsprechenden Hardware und software) diese Sicherungen einzeln durchbrennen und damit die Leitung unterbrechen. Auf diese Weise lassen sich spezielle UND-Schaltungen (die sogenannten Produkt-Terme, P-Terme) in den PLDs erzeugen. Nachgeschaltet zu den UND-Gattern finden sich dann ODER-Gatter ('OR-Gates'). Jedes ODER-Gatter ist mit jedem der vorausgehenden 50 UND-Gattern verbunden. Auch hier gibt es für jede einzelne Leitung die Möglichkeit,diese zu unterbrechen um auf diese Weise spezielle Funktionen zu erzeugen. Mit den ODER-Gattern wird dann sozusagen die Summe aller Produkte ('SOP := Sum Of Products') gebildet.

Da in der vorausgehenden Vorlesung dargelegt worden ist, dass man mit den boolschen Funktionen 'NOT (~)', 'AND (&)' sowie 'OR (+)' alle anderen boolschen Funktionen definieren lassen, ist es also mit diesen PLDs mögliche, jede boolsche Schaltfunktion auf diese Weise zu realisieren.

Programmierbarer Logik Array (PLA)

Es sei hier nur angemerkt, dass auf der Basis der soeben geschilderten PAL-Struktur zusätzliche Komplexitäten realisiert werden, indem die Ausgänge der PAL-Struktur mit Flip-Flops (s.u.) kombiniert werden, deren Ausgänge zugleich auch auf die Eingänge des Bausteins rückgekoppelt werden. Dadurch lassen sich sogenannte Sequencer, sprich sequentielle Zustandsmaschinen (Moore- oder Mealy-Automaten) realisieren. Statt UND-Gatter werden auch NAND-Gatter verwendet.

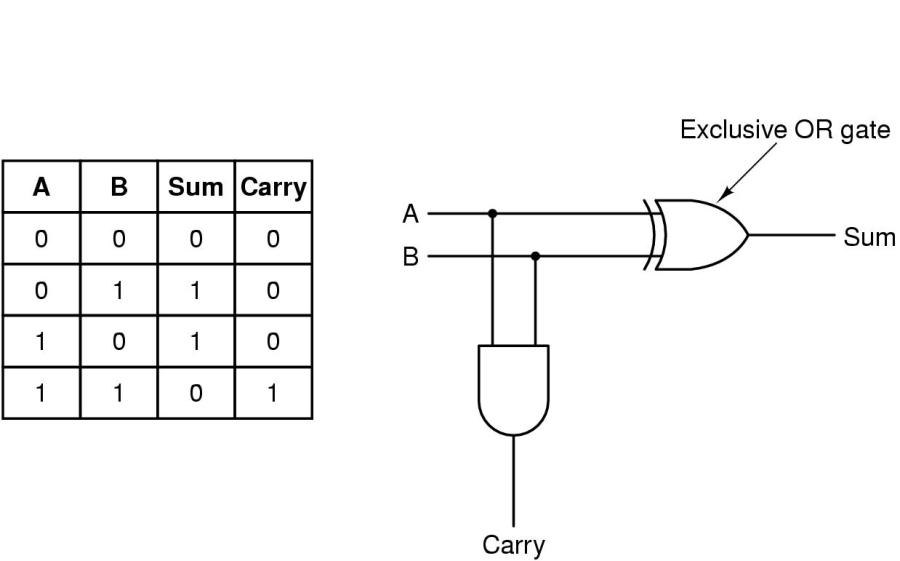

Von einem Mikroprozessor erwartet man, dass er logische und arithmetische Operationen mit binaeren Zahlen ausführen kann. Im folgenden wird dies am Beispiel einfacherer Addierer untersucht.

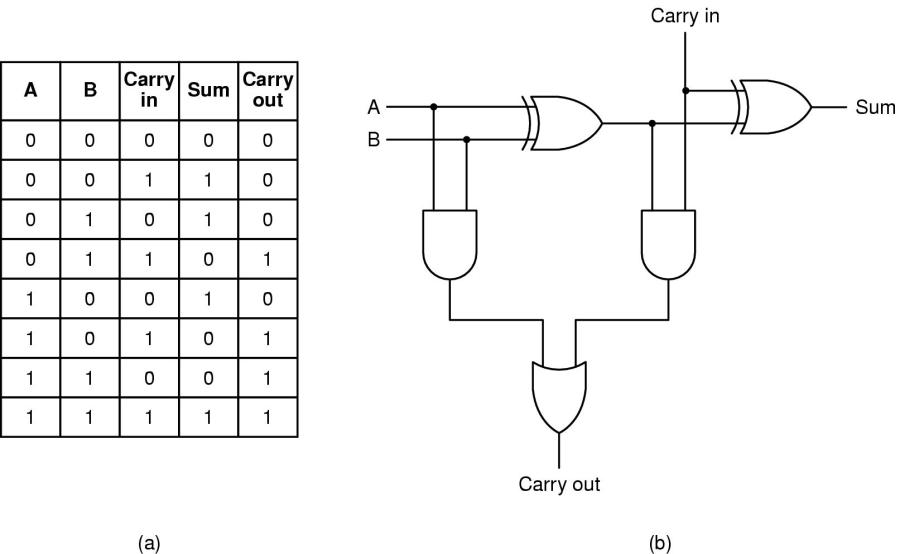

Im Halbaddierer werden zwei Variablen A und B mit jeweils 1 Bit addiert. Die Wahrheitswerttabelle beschreibt die Funktion dieser Schaltung. Diese Schaltung ist noch nicht skalierbar.

Halbaddierer

Interessanter ist die Erweiterung des Halbaddierers zum Volladdierer. In dieser Schaltung wird berücksichtigt, dass es schon ein Übertrags-Bit ('Carry-Bit') aus einer vorausgehenden Operation geben kann. Damit ist diese Schaltung dazu geeignet, parallel geschaltet zu werden, um auf diese Weise eine n-Bit-Addition zu ermöglichen.

Eine Parallelschaltung dieses Volladdierers wird Ripple-Carry-Addierer (RCA) genannt. Er hat nur den Nachteil, dass das Ergebnis erst dann voll zur Verfügung steht, wenn das Carry-Bit alle beteiligten Gatter durchlaufen hat. Von diesem 'wellenartigen' (engl. 'ripple') Durchlaufen aller beteiligten Addierstufen hat diese Architektur ihren Namen. Für weitere Formen von Addierern und anderen formen von arithmetischen Operationen siehe [MÄRTIN 2001:110ff]).

Volladdierer

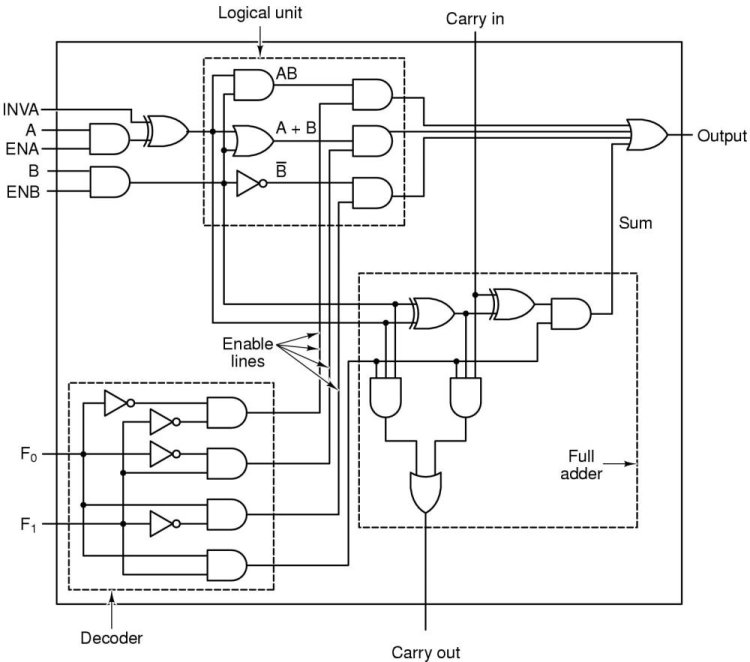

Mit dem bisherigen Wissen um Adressierung und Addieren lässt sich schon eine einfache arithmetische logische Recheneinheit (' ALU := Arithmetical Logical Unit') realisieren.

Die folgende Grafik zeigt eine 1-Bit ALU, die sich mit anderen 1-Bit-ALUs zusammenschalten lässt. Sie bietet insgesamt 4 Funktionen an: 'AB' (logisch), 'A + B', '~B' sowie 'AB' (arithmetisch). Die eingangssignale kommen über die Eingänge A,B sowie der Invertierung von A mit INVA. Zusätzlich gibt es die signale 'ENA' bzw. 'ENB' für Enable A bzw. B.

Die Auswahl der vier verschiedenen Funktionen geschieht über die Adressleitungen F0, F1. Das arithmetische Addieren wird mittels der Volladdierer-Schaltung realisiert, die kurz zuvor vorgestellt worden ist.

Arithmetisch Logische Einheit (ALU)

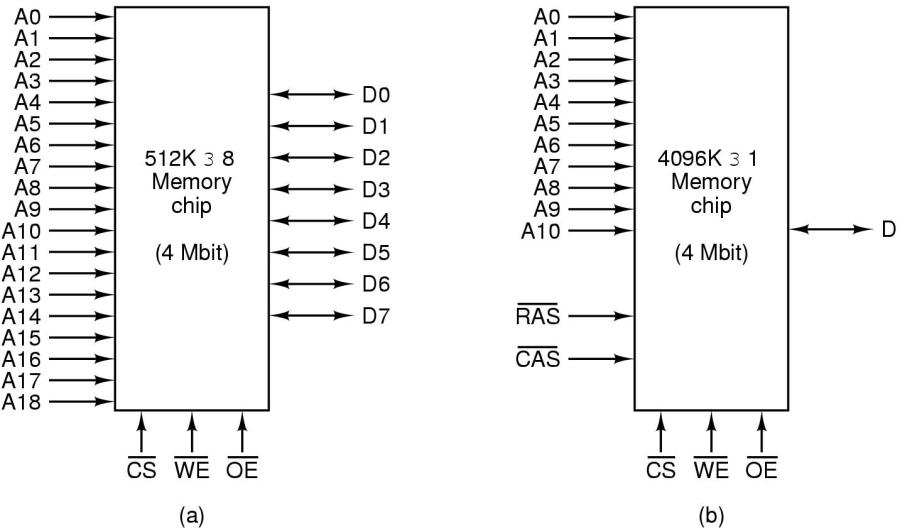

Hier soll nun das Prinzip der Datenspeicherung erläutert werden. Die nächste Schaltung zeigt zwei typische Speicherchips, wie man sie fertig konfiguriert kaufen kann. Als erstes muss man mittels Chip-Select ~CS den Chip selektieren. Dann muss man über Adressleitungen ein bestimmtes n-Bit-Muster (im Beispiel entweder n=8 oder n=1) selektieren; dies geschieht in zwei Schritten: (i) zuerst wird mit ~RAS (ROW Address Strobe) eine Zeile, dann mit ~CAS (Column Address Strobe) eine Spalte selektiert. Dann schreibt man entweder ein n-Bit-Muster in den Chip mittels Write-Enable ~WE oder man liest ein n-Bitmuster aus der selektierten Stelle mittels Output-Enable ~OE aus. Diese Schaltung verrät allerdings nichts über die Schaltungen, mittels denen dieser Chip realisiert wurde.

Speicherchips

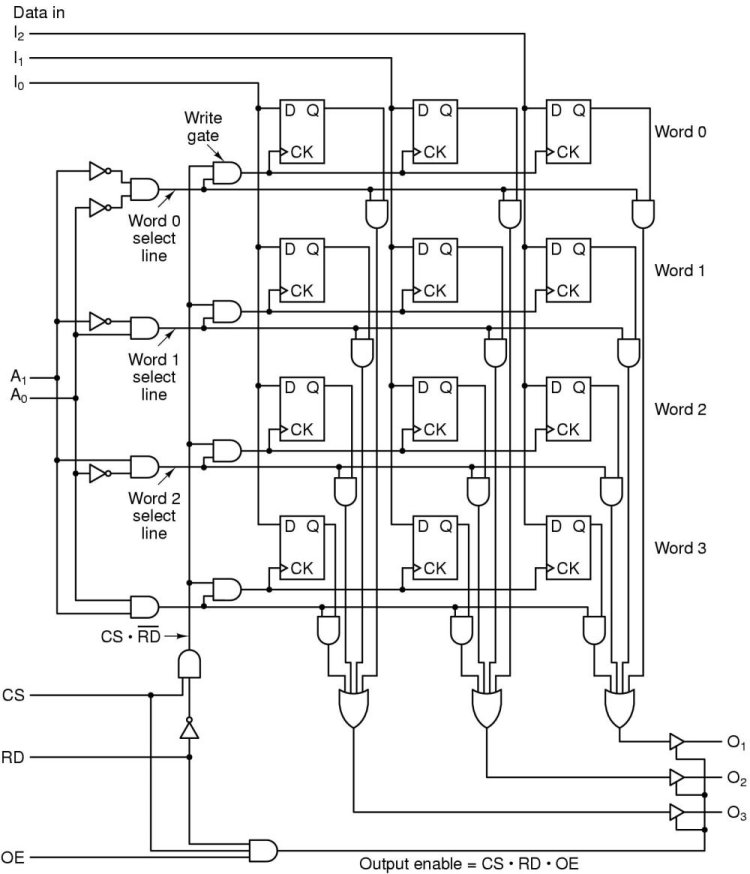

Hinweise auf eine mögliche Architektur enthält die nächste Schaltung. Hier sieht man eine Prinzipschaltung für einen Speicher mit vier 3-Bit-Worten. Es gibt drei Inputleitungen I0, .., I2 , drei Outputleitungen O0, .., O2 , zwei Adressleitungen A0, A1 zum Selektieren eines der Worte sowie drei Steuerleitungen Chip-Select CS, Read RD für Lesen oder ~RD für Schreiben sowie Output-Enable OE.

Beispiel eines Schreibvorganges: CS=1 und RD=0 lassen das UND-Gatter mit CS.~RD auf High gehen. Wenn gleichzeitig die Adressleitungen ein bestimmtes 3-Bit-Wort ausgewählt haben, dann gibt es ein UND-Gatter das von L auf H geht und am CLK-Eingang der D-FlipFlops anliegt. Wenn jetzt Daten an den Inputeingängen anliegen werden diese im Moment des Flankenanstieges übernommen. Dies bedeutet, die Daten und Adressen müssen schon anliegen, bevor CS.~RD erfolgen.

Beispiel eines Lesevorganges: Beim Lesevorgang müssen keine Daten anliegen. Es müssen allerdings wieder die Adressleitungen ein 3-Bit-Wort auswählen und für die Steuerleitungen gilt: CS=1 & RD=1 & OE=1. Damit ist die Datenaufnahme blockiert, aber die Datenausgabe freigegeben. Insofern ein selektiertes Wort auf Q H-Werte hat, werden diese dann auf die Ausgangsleitungen ausgegeben.

Alle Elemente in dieser Schaltung sind bisher schon bekannt bis auf die nichtinvertierenden Puffer am Ausgang und die Flip-Flops in den 3-Bit-Speicherschaltungen. Ein nichtinvertierender Puffer verhält sich bei Freischaltung wie ein normaler Schalter, bei nicht Freischaltung wie ein unterbrochener Schalter. Die Flip-Flops in der Schaltung haben einen Dateneingang auf D, dessen signal bei der aufsteigenden Flanke beim Eingang CLK übernommen wird und dann solange an Q zur Verfügung steht, bis mit CLK-Rise ein neues Signal an D übernommen wird.

4x3 Speicher

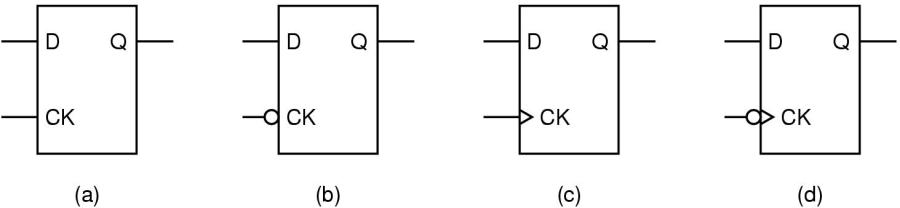

Interessant sind die Flip-Flop-Schaltungen. Die folgende Grafik stellt vier wichtige Typen vor: Typ (a) ist ein sogenanntes Latch, das die Daten an D übernimmt, wenn CK H ist, Typ (b), wenn CK L ist. Typ (c) bei ansteigender Flanke, und Typ (d) stellt ein Flip-Flop dar, das die Daten an D auf der fallenden Flanke übernimmt.

Latches und Flip-Flops

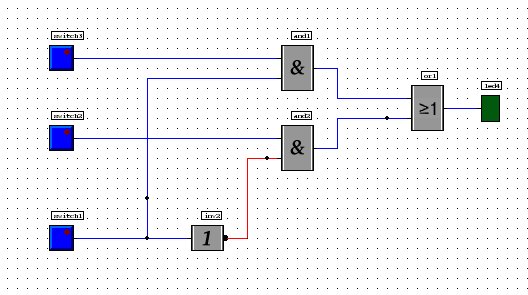

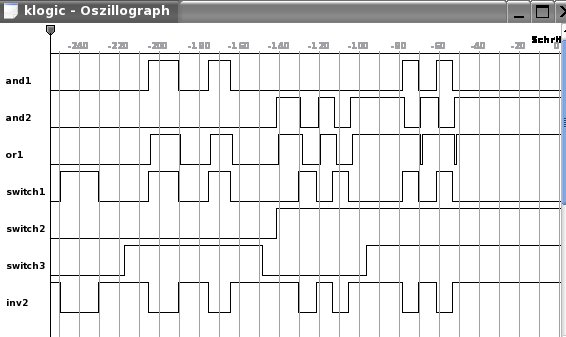

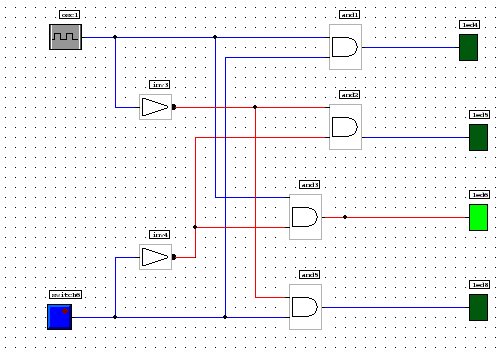

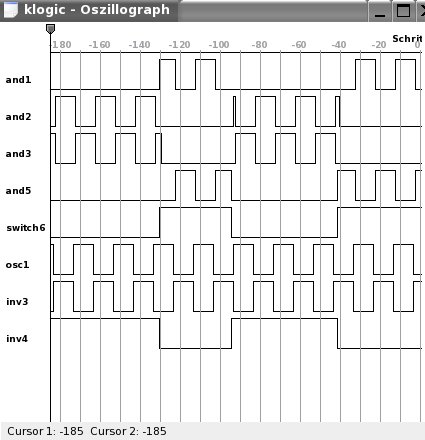

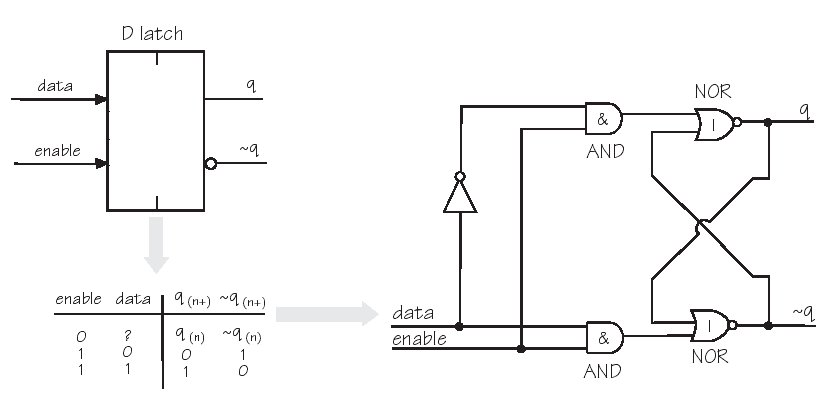

Das folgende Diagramm zeigt das Beispiel eines D-Flip-Flops, das mit aufsteigender Flanke getaktet wird. Zugleich ist eine mögliche Ersatzschaltung angegeben, mit der man solch ein D-FlipFlop realisieren könnte.

D-Flip-Flop getaktet mit ansteigender Flanke

D-Flip-Flop getaktet mit steigender Flanke

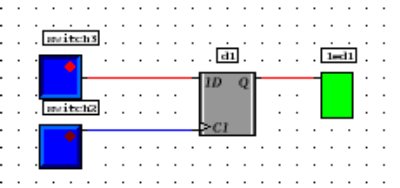

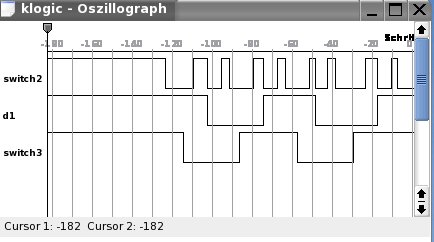

Signalverlauf eines D-Flip-Flop mit fallender Flanke

(Anmerkung: dass der Signallaufplan mit fallender Flanke arbeitet während die Schaltung ein D-Flipflop mit steigender Flanke enthält ist ein Artefakt des klogic-Simulators; es zeigt sich, dass das Verhalten des Simulators nicht korrekt die Einstellungen reproduziert)

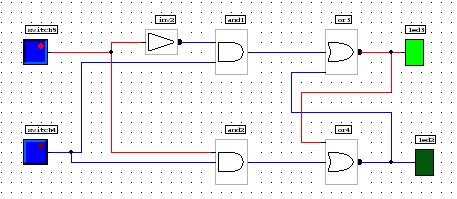

Die Ersatzschaltung für das D-Flipflop besteht grob aus zwei Teilen: einer Endstufe bestehend aus einem RS-Latch und einer Vorstufe bestehend aus zwei UND-Gattern.

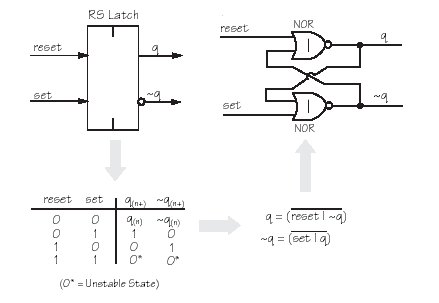

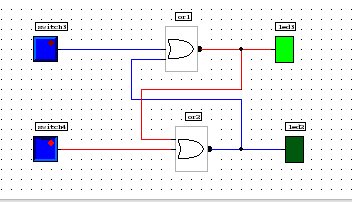

RS-Latch mit NORs

RS-Latch mit NORs

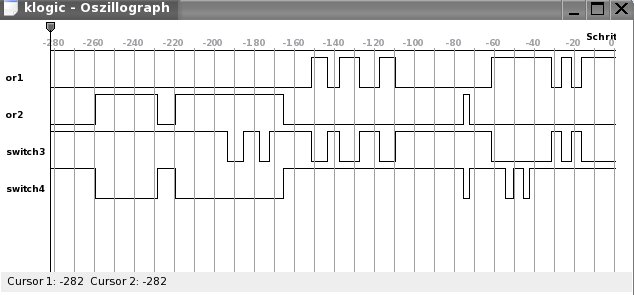

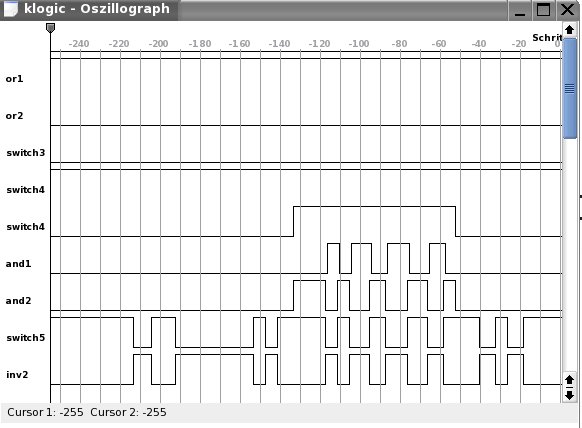

Signalverlauf bei RS-Latch

Man kann erkennen, dass der Signalverlauf am Ausgang Q dem Signalverlauf am Eingang switch3 invertiert entspricht, wenn Eingang switch 4 auf High liegt.

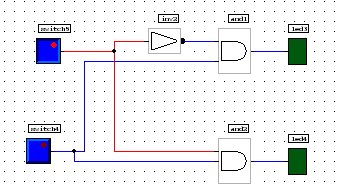

Vorstufe D-Flipflop

Vorstufe D-Flipflop Signalverlauf

Man kann gut erkennen, dass Eingang switch4 enable ist; nur wenn switch4 auf high liegt, werden die Daten durchgereicht.

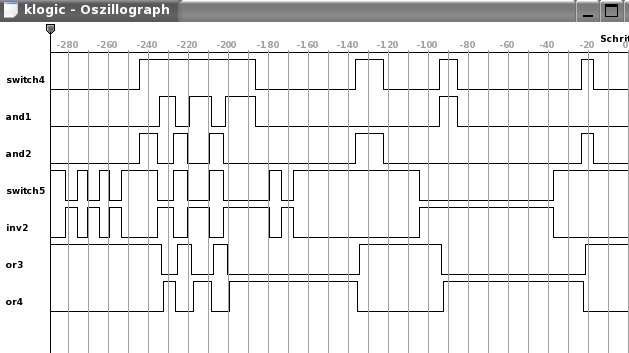

Synthese D-Flipflop

Synthese D-Flipflop Signalverlauf

Bei switch4 enabled folgt der Ausgang Q dem Eingang switch5. Dies kann man dann nutzen, um mit dem Eingang switch4 mit der steigenden Flanke den Wert an Eingang switch5 zu übernehmen.

Versuchen Sie in dem Text Antworten auf folgende Aufgaben zu formulieren:

Konstruieren Sie eine Schaltung mittels dem oben vorgestellten PAL. Ersetzen Sie in der PAL-Schaltung die UND-Gatter durch NAND-Gatter und untersuchen Sie, wie sich die Schaltung mit dieser Anordnung realisieren lässt.

Wie kann man mittels des in der Vorlesung vorgestellten 1-Bit-Volladdierers einen 3-Bit-Volladdierer realisieren?

Wie kann man mittels der in der Vorlesung vorgestellten 1-Bit-ALU eine 3-Bit-ALU realisieren?

Es wurde das Verhalten eines D-Flip-Flops gezeigt, das mit ansteigender Flanke getaktet ist. Versuchen Sie eine Schaltung anzugeben, die nur Standardgatter enthält und die solch ein Verhalten reproduziert.